Marconi Applied Technologies CCD05-20 Series Scientific Image Sensor Large Area, Slow Scan CCD Image Sensor

#### FEATURES

- 770 (H) x 1152 (V) pixel format

- 17.3 x 26 mm active area

- Extremely low pixel readout noise

- Visible light and X-ray sensitive

- Two readout registers

- Uniform response over whole image area

- Two low noise amplifiers for slow-scan systems and two large signal amplifiers for high speed applications

- Symmetrical anti-static gate protection

- Long life expectancy

- Low voltage operation

- Radiation tolerant

#### DESCRIPTION

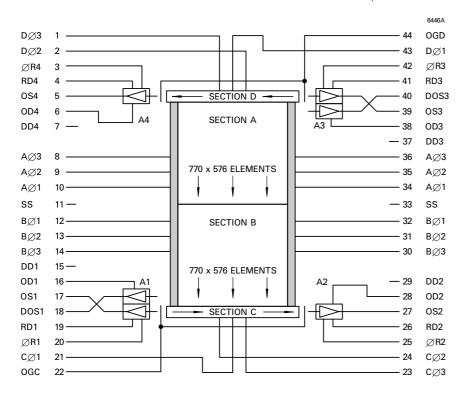

The CCD05-20 series scientific image sensor is one of the CCD05 range of very large area CCD image sensors primarily intended to suit the requirements of astronomy, medical diagnostic and scientific measuring instruments. The pixel structure is based on the long established and highly successful CCD01-06 series of scientific sensors (originally type P8603), with three-level polysilicon electrode technology, three phase clocking and buried channel charge transfer. Readout registers are incorporated above and below the image area. Each register has at one end a high performance low noise amplifier for slow scan applications and at the other end a high speed amplifier. The image area is also split into two sections, each of which can be clocked separately.

The CCD05-20 series scientific image sensor is primarily specified for operation in a full frame imaging mode with slow scan readout from the whole image area through either of the low noise amplifiers and is tested at a temperature of 140 K.

Other operating modes are also possible, including use of the high speed amplifiers (but at higher noise), split readout simultaneously through both registers and pixel binning. A frame transfer mode version is available, as described in the CCD05-20-Y-256 scientific image sensor data sheet. Potential users are invited to discuss their applications with Marconi Applied Technologies to ensure optimum performance.

# **GENERAL DATA**

| Image region (section A)         |   | 770(H) x 576   | pixels |

|----------------------------------|---|----------------|--------|

| Image region (section B)         |   | 770(H) x 576   | pixels |

| Image area (sections A + B) .    |   | . 17.3 x 25.92 | mm     |

| Pixel pitch (row and column) .   |   | . 22.5 x 22.5  | μm     |

| Responsivity at 700 nm (typical) |   | 250            | mA/W   |

| Spectral response range          | - | . 420 - 1050   | nm     |

| Deeleene                         |   |                |        |

#### Package

| •                  |     |     |      |     |     |   |                       |

|--------------------|-----|-----|------|-----|-----|---|-----------------------|

| Outline dimensions | s.  |     |      |     |     |   | 45.7 x 33.0 mm        |

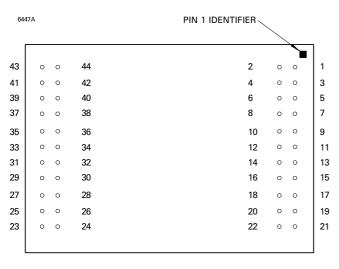

| Number of pins .   |     |     |      |     |     |   | 44                    |

| Inter-pin spacing  |     |     |      |     |     |   | . 2.54 mm (0.1 inch)  |

| Inter-row spacing  |     |     |      |     |     |   | . 2.54 mm (0.1 inch)  |

| Inner row spacing  | (ac | ros | s se | ens | or) |   | . 35.56 mm (1.4 inch) |

| Window             |     |     | •    |     |     | · | removable glass       |

| Mounting position  |     |     | •    |     |     | · | any                   |

|                    |     |     |      |     |     |   |                       |

The device and its package is nearly symmetrical and care must be taken that it is correctly inserted. Pin 1 on the package is spot marked for this purpose.

In the event of damage to the readout amplifier, then depending on the nature and extent of the damage, operation may be resumed by using the alternative readout register (making the necessary wiring changes advised in notes 10, 12 and 14).

Marconi Applied Technologies recommends the following zero insertion force grid ZIF socket manufactured by 3M Textool. The grid matrix is  $17 \times 17$  with catalogue number 2xxx-6317-70-1900. The contacts are nickel-boron 300-2740-06-0005.

#### HANDLING CCD SENSORS

CCD sensors, in common with most high performance IC devices, are static sensitive. In certain cases a static electricity discharge may destroy or irreversibly degrade the device. Accordingly, full anti-static handling precautions should be taken whenever using a CCD sensor or module. These include:

- Working at a fully grounded workbench

- Operator wearing a grounded wrist strap

- All receiving socket pins to be positively grounded

- Unattended CCD's should not be left out of their conducting foam or socket.

All devices are provided with internal protection circuits to the gate electrodes.

For scientific use the device should not be cooled faster than 5  $^\circ\mathrm{C}$  per minute.

Evidence of incorrect handling will invalidate the warranty.

Marconi Applied Technologies Limited, Waterhouse Lane, Chelmsford, Essex CM1 2QU England Telephone: +44 (0)1245 493493 Facsimile: +44 (0)1245 492492 e-mail: info@eev.com Internet: www.marconitech.com Holding Company: Marconi p.l.c.

Marconi Applied Technologies Inc. 4 Westchester Plaza, PO Box 1482, Elmsford, NY10523-1482 USA Telephone: (914) 592-6050 Facsimile: (914) 592-5148 e-mail: info@eevinc.com

## **MAXIMUM RATINGS (Absolute values)**

Voltages with respect to  $V_{SS}$  (pins 11 and 33):

| Voltages with res            | spe | ct   | to   | Vs   | s (  | pin | ns 11 | 1 a | nd | 33 | 3): |      |             |     |    |

|------------------------------|-----|------|------|------|------|-----|-------|-----|----|----|-----|------|-------------|-----|----|

| pin 1 (DØ3) .                |     |      | •    | •    | ·    | •   |       |     |    |    |     |      | $\pm 2$     |     | V  |

| pin 2 (DØ2) .                |     |      |      |      |      | •   |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| pin 3 (ØR4) .                |     |      |      |      |      | •   |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| pin 4 (RD4) .                |     |      |      |      |      |     |       |     |    |    |     | 3 to |             |     | V  |

| pin 5 (OS4) .                |     |      |      |      |      |     |       |     |    | _  | 0.3 | 3 to | +2          | 25  | V  |

| pin 6 (OD4) .                |     |      |      |      |      |     |       |     |    | _  | 0.3 | 3 to | +2          | 25  | V  |

| pin 7 (DD4) .                |     |      |      |      |      |     |       |     |    | _  | 0.3 | 3 to | +2          | 25  | V  |

| pin 8 (AØ3) .                |     |      |      |      |      |     |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| pin 9 (AØ2) .                |     |      |      |      |      |     |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| pin 10 (AØ1)                 |     |      |      |      |      |     |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| pin 12 (BØ1)                 |     |      |      |      |      |     |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| pin 13 (BØ2)                 |     |      |      |      |      |     |       |     |    |    |     |      | +2          | 20  | V  |

| pin 14 (BØ3)                 |     |      |      |      |      |     |       |     |    |    |     |      | +2          | 20  | V  |

| pin 15 (DD1)                 |     |      |      |      |      |     |       |     |    | _  | 0.3 | 3 to | +2          | 25  | V  |

| pin 16 (0D1/D                |     |      |      |      |      |     |       |     |    | _  | 0.3 | 3 to | +2          | 25  | V  |

| pin 17 (OS1)                 |     |      |      | ÷    |      | ÷   |       | ÷   |    |    |     | 3 to |             |     | v  |

| pin 18 (DOS1)                |     |      |      | ÷    |      | ż   |       |     |    |    |     | 3 to |             |     | v  |

| pin 19 (RD1)                 |     |      |      |      |      |     |       |     |    |    |     | 3 to |             |     | v  |

| pin 10 (MB1)                 | •   |      |      | •    |      |     |       |     |    |    |     |      | +2          |     | v  |

| pin 20 (Ø11)                 |     | •    | •    | •    | •    | •   | •     | •   |    |    |     |      | +2+2        |     | v  |

| pin 21 (Cg) ()               |     |      | •    | •    | •    | •   | •     | •   | •  | •  |     |      | $\pm 2$     |     | v  |

| pin 22 (00C)                 | •   |      | •    | •    | ·    | ·   | •     |     |    |    |     |      | $\pm 2 + 2$ |     | V  |

| pin 23 (CØ3)<br>pin 24 (CØ2) |     | •    | •    | •    | ·    | ·   | •     | ·   | •  |    |     |      | $\pm 2 + 2$ |     | V  |

| pin 24 (CØ2)<br>pin 25 (ØR2) |     | •    | •    | •    | ·    | ·   | •     | •   |    |    |     |      | $\pm 2 + 2$ |     | V  |

| pin 25 (@R2)<br>pin 26 (RD2) |     | •    | •    | ·    | ·    | ·   |       | ·   |    |    |     | 3 to |             |     | -  |

|                              | •   | •    | ·    | •    | ·    | ·   | ·     | ·   |    | _  | 0.  | 3 lO | +2          | 20  | V  |

| pin 27 (OS2)                 |     | •    | •    | •    | ·    | ·   | ·     | ·   |    |    |     | 3 to |             |     | V  |

| pin 28 (OD2)                 |     | •    | ·    | ·    | ·    | ·   | ·     | ·   |    |    |     | 3 to |             |     | V  |

| pin 29 (DD2)                 |     |      | ·    | •    | ·    | ·   |       | ·   |    |    |     | 3 to |             |     | V  |

| pin 30 (BØ3)                 |     | •    | ·    | ·    | ·    | ·   | ·     | •   | ·  | ·  | •   |      | $\pm 2$     |     | V  |

| pin 31 (BØ2)                 |     | •    | ·    | ·    | ·    | ·   | ·     | ·   | ·  | ·  | •   |      | $\pm 2$     |     | V  |

| pin 32 (BØ1)                 |     | •    | ·    | ·    | ·    | ·   | •     | ·   | ·  | ·  | •   |      | $\pm 2$     |     | V  |

| pin 34 (AØ1)                 |     | •    | •    | ·    | ·    | ·   | •     | ·   | ·  | ·  | •   |      | $\pm 2$     |     | V  |

| pin 35 (AØ2)                 |     | •    | •    |      | ·    | ·   |       | •   | ·  | ·  |     |      | $\pm 2$     |     | V  |

| pin 36 (AØ3)                 |     | •    |      |      |      |     |       |     |    |    |     |      | $\pm 2$     |     | V  |

| pin 37 (DD3)                 |     |      |      |      | •    |     |       |     |    |    |     | 3 to |             |     | V  |

| pin 38 (OD3/E                | 00  | D3)  | )    |      |      |     | •     | •   |    | _  | 0.  | 3 to | +2          | 25  | V  |

| pin 39 (OS3)                 |     |      |      |      |      |     |       |     |    | _  | 0.  | 3 to | +2          | 25  | V  |

| pin 40 (DOS3)                |     | •    |      |      |      |     |       |     |    | _  | 0.  | 3 to | +2          | 25  | V  |

| pin 41 (RD3)                 |     |      |      |      |      |     |       |     |    |    | 0.  | 3 to | +2          | 25  | V  |

| pin 42 (ØR3)                 |     |      |      |      |      |     |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| pin 43 (DØ1)                 |     |      |      |      |      |     |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| pin 44 (OGD)                 |     |      |      |      |      |     |       |     |    |    |     |      | $\pm 2$     | 20  | V  |

| Voltages betwee              | n p | bair | s o  | of p | oins | s:  |       |     |    |    |     |      |             |     |    |

| pin 5 (OS4) to               | pi  | n 6  | i (C | DD4  | 1)   |     |       |     |    |    |     |      | ±´          | 15  | V  |

| pin 16 (OD1/E                |     | D1)  | ) to | o pi | 'n   | 17  | (OS   | 1)  |    |    |     |      | ±´          | 15  | V  |

| ,<br>pin 16 (OD1/E           |     |      |      |      |      |     |       |     |    |    |     |      | + ′         |     | V  |

| pin 27 (OS2) t               |     |      |      |      |      |     |       |     |    |    |     |      | _<br>+ ´    |     | V  |

| pin 38 (OD3/E                |     |      |      |      |      |     |       |     |    |    |     |      | ÷<br>+ ´    |     | V  |

| pin 38 (OD3/E                |     |      |      |      |      |     |       |     |    |    |     |      | ÷<br>+ ´    |     | V  |

| Current through              |     |      |      |      |      |     |       |     |    |    |     |      | _           | 10  | mA |

| sanon inough                 | un  | , 3  | Ju   |      |      | a   | ann   | РП  | •  | •  | •   | •    |             | . • |    |

## **HIGH ENERGY RADIATION**

Device parameters may begin to change if subject to an ionising dose of greater than  $10^4 \mbox{ rads}.$

Certain characterisation data are held at Marconi Applied Technologies. Users planning to use CCDs in a high radiation environment are advised to contact Marconi Applied Technologies.

# **OPERATING CHARACTERISTICS**

| r                                  | Min   | Typical | Max |   |

|------------------------------------|-------|---------|-----|---|

| Storage temperature                |       |         |     |   |

| (non-operating) 2                  | 233   | -       | 373 | Κ |

| Operating temperature (dry atmosph | nere) |         |     |   |

| (see notes 1 and 2)                | 73    | 140     | 233 | Κ |

# **PERFORMANCE** (Front face illuminated)

|                                                               |          | umma       | .eu/       |

|---------------------------------------------------------------|----------|------------|------------|

|                                                               | Min      | Typical    | Max        |

| Peak signal, e <sup>-</sup> /element                          |          |            |            |

| (see note 3)                                                  | 300k     | 500k       | -          |

| Dark signal, e <sup>-</sup> /element/s                        |          |            |            |

| (see note 4)                                                  |          | 20k        | 50k        |

| Charge transfer efficiency, %                                 | 00.00    | 005        |            |

| (parallel register) (see note 5) .<br>Response non-uniformity | . 99.93  | - 080      | -          |

| (% of mean)                                                   | _        | +3         | + 10       |

| Dark signal non-uniformity                                    | •        | <u> </u>   | <u> </u>   |

| (% of mean)                                                   |          | <u>+</u> 2 | <u>+</u> 5 |

| Sensitivity, $\mu$ V/e <sup>-</sup> :                         |          |            |            |

| low noise amplifier                                           |          | 2.0        | -          |

| high speed amplifier                                          |          | 0.6        | -          |

| Output register capacity (relative to i                       | mage se  | ctions):   |            |

| towards low noise amplifier                                   |          | 1.1        | -          |

| towards high speed amplifier .                                |          | 3.0        | -          |

| Line transfer time, µs                                        |          | -          | -          |

| Maximum readout frequency, MHz (                              | see note | 96):       |            |

| low noise amplifier                                           | . 5.0    | -          | -          |

| high speed amplifier                                          | . 15     | -          | -          |

| Readout noise, rms e <sup>-</sup> /pixel                      |          |            |            |

| at 140 K (see note 7):                                        |          | 0          | 0          |

| grade 0 ('super')                                             |          | 6          | 8          |

| grade 1                                                       |          | 8          | 10         |

## **BLEMISH SPECIFICATION (See note 8)**

White column A white column is counted if its amplitude is >5% of the saturation level with no illumination on the sensor, at 230 K after 30 seconds using Marconi Applied Technologies slow scan equipment.

Traps Traps must be visible at the 200 e<sup>-</sup> level.

Slipped columns Must be visible at 200 e<sup>-</sup> level.

**Black spots** >10% contrast at  $^{1}/_{2}$  saturation. 230 K, 30 s integration time, Marconi Applied Technologies slow scan equipment.

*White spots* A white spot exists when it exceeds 5% of the saturation level, with no illumination on the sensor, at 230 K after 30 s in Marconi Applied Technologies slow scan equipment.

| Grade            |                                                    | 0                | 1                | 2                  |

|------------------|----------------------------------------------------|------------------|------------------|--------------------|

| Column defects   | - black or slipped<br>- white                      | 0<br>0           | 2<br>0           | 6<br>0             |

| Black spots      | <3 pixels<br><5 pixels<br><10 pixels<br>>10 pixels | 4<br>2<br>0<br>0 | 6<br>4<br>0<br>0 | 30<br>16<br>2<br>0 |

| $Trap > 200 e^-$ |                                                    | 2                | 5                | 12                 |

| White spots      |                                                    | 26               | 26               | 40                 |

Minimum separation between adjacent black columns 50 pixels.

# OPERATING VOLTAGES (See notes 9 and 15)

|          |             |                                                             | Pulse amplitude<br>or DC level (V) |              |          |

|----------|-------------|-------------------------------------------------------------|------------------------------------|--------------|----------|

| Pin      | Ref         | Connection                                                  | Min                                | Typ          | Max      |

|          |             |                                                             |                                    | 715          |          |

| 1        | DØ3         | D register readout (see note 10)                            | 8                                  | 10           | 15       |

| 2        | DØ2         | D register readout (see note 10)                            | 8                                  | 10           | 15       |

| 3        | ØR4         | output reset pulse (A4)                                     | 8                                  | 10           | 15       |

| 4        | RD4         | reset transistor drain (A4)                                 | 15                                 | 17           | 19       |

| 5        | OS4         | output transistor source (A4)                               |                                    | e note 1     |          |

| 6        | OD4         | output transistor drain (A4)                                | 25                                 | 26           | 30       |

| 7        | DD4         | diode drain                                                 | 20                                 | 22           | 25       |

| 8        | AØ3         | section A                                                   |                                    |              | . –      |

| 9        | AØ2         | drive pulses                                                | 8                                  | 10           | 15       |

| 10       | AØ1         | (see note 12)                                               | 0                                  | 0            | 10       |

| 11       | SS          | substrate                                                   | 0                                  | 6            | 10       |

| 12       | BØ1         | section B                                                   | 0                                  | 10           | 45       |

| 13       | BØ2         | drive pulses                                                | 8                                  | 10           | 15       |

| 14       | BØ3         | (see note 12)                                               | 00                                 | 00           | 05       |

| 15       | DD1         | diode drain                                                 | 20                                 | 22           | 25       |

| 16       | OD1         | output drain (A1)                                           | 20                                 | 22           | 25       |

| 17       | DOD1        | dummy output drain (A1)                                     | 20                                 | 22           | 25       |

| 17       | 0S1         | output transistor source (A1)                               |                                    | e note 1     |          |

| 18<br>10 | DOS1<br>RD1 | dummy output source (A1)                                    |                                    | note 1<br>17 |          |

| 19<br>20 | ØR1         | reset transistor drain (A1)                                 | 15<br>8                            | 10           | 19<br>15 |

| 20<br>21 | /0          | output reset pulse (A1)<br>C register readout (see note 14) | o<br>8                             | 10           | 15       |

| 21<br>22 | CØ1<br>OGC  | 0                                                           | 0<br>1                             | 2            | 5        |

| 22<br>23 | CØ3         | C register output gate<br>C register readout (see note 14)  | 8                                  | 10           | 5<br>15  |

| 23<br>24 | CØ3<br>CØ2  | C register readout (see note 14)                            | 8                                  | 10           | 15       |

| 24<br>25 | ØR2         | output reset pulse (A2)                                     | 8                                  | 10           | 15       |

| 26       | RD2         | reset transistor drain (A2)                                 | 15                                 | 17           | 22       |

| 20       | OS2         | output transistor source (A2)                               |                                    | e note 1     |          |

| 28       | 002<br>0D2  | output transistor drain (A2)                                | 25                                 | 26           | 30       |

| 29       | DD2         | diode drain                                                 | 20                                 | 22           | 25       |

| 30       | BØ3         | section B                                                   | 20                                 | 22           | 20       |

| 31       | BØ2         | drive pulses                                                | 8                                  | 10           | 15       |

| 32       | BØ1         | (see note 12)                                               | Ū                                  | 10           | 10       |

| 33       | SS          | substrate                                                   | 0                                  | 6            | 10       |

| 34       | AØ1         | section A                                                   | 0                                  | 0            | 10       |

| 35       | AØ2         | drive pulses                                                | 8                                  | 10           | 15       |

| 36       | AØ3         | (see note 12)                                               | -                                  |              |          |

| 37       | DD3         | diode drain                                                 | 20                                 | 22           | 25       |

| (        | OD3         | output drain (A3)                                           | 20                                 | 22           | 25       |

| 38{      | DOD3        | dummy output drain (A3)                                     | 20                                 | 22           | 25       |

| 39       | OS3         | output transistor source (A3)                               |                                    | e note 1     |          |

| 40       | DOS3        | dummy output source (A3)                                    |                                    | e note '     |          |

| 41       | RD3         | reset transistor drain (A3)                                 | 15                                 | 17           | 19       |

| 42       | ØR3         | output reset pulse (A3)                                     | 8                                  | 10           | 15       |

| 43       | DØ1         | D register readout (see note 10)                            | 8                                  | 10           | 15       |

| 44       | OGD         | D register output gate                                      | 1                                  | 2            | 5        |

# NOTES

- 1. The recommended operating temperature for optimum performance is 140 K.

- 2. Operation at up to 338 K is possible for high speed applications.

- 3. Signal level at which resolution begins to degrade.

- 4. Measured at 293 K. Dark signal at any temperature T (kelvin) may be estimated from:

$$Q_d / Q_{d0} = 122 T^3 e^{-6400/T}$$

where  $Q_{d0}$  is the dark signal at T = 293 K (20 °C).

- Measurements made using charge generated by X-ray photons of known energy. In practice, the horizontal and vertical charge transfer efficiency is assessed qualitatively on a video monitor. A white on black grid pattern is displayed at a signal level of 200 e<sup>-</sup>/pixel.

- 6. This is largely a practical limit set by difficulties in providing high speed drive pulses and sufficient output bandwidth.

- 7. Measured using a dual-slope integrator technique (i.e. correlated double sampling) with a 10  $\mu s$  integration period.

- 8. Blemishes are assessed at a signal level of 1000  $e^-/{\rm pixel.}$

- 9. Tie all unused RD, OD, OS and DOS to  $V_{\text{OD}};$  OG to  $V_{\text{OG}};$   $\not{\mbox{${\cal O}$}}$  R to 0 V.

- 10. Readout through amplifier 4 shown; for readout through amplifier 3,  $D\emptyset1$  and  $D\emptyset2$  should be interchanged.

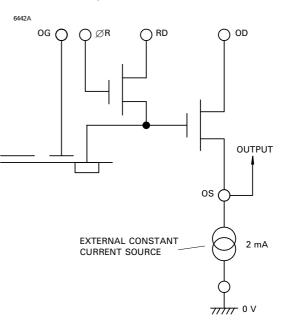

- 11. With a 2 mA constant current load V\_{OS} = V\_{RD} + 6 V.

- 12. Readout through section C register shown; for readout through section D register,  $\emptyset 1$  and  $\emptyset 2$  should be interchanged.

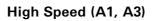

- 13. With 3.3 k $\Omega$  load resistors, V\_{OS} = V\_{DOS} = V\_{RD} 3 V.

- 14. Readout through amplifier 2 shown; for readout through amplifier 1,  $C\emptyset1$  and  $C\emptyset2$  should be interchanged.

- 15. All pulse low levels  $\pm 1$  V.

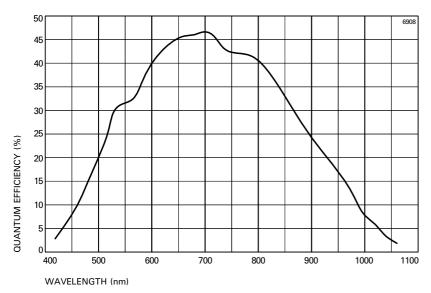

# **TYPICAL SPECTRAL RESPONSE**

# SCHEMATICS

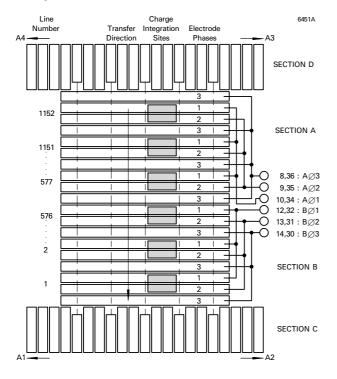

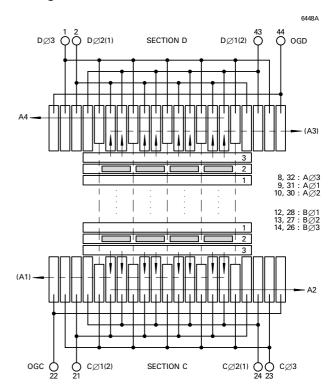

Arrows show direction of charge transfer with clock phases connected as shown; the direction of charge transfer in any section can be changed by transposing the  $\emptyset$ 1 and  $\emptyset$ 2 connections.

Charge collection is shown with both  $\emptyset$ 1 and  $\emptyset$ 2 electrodes held at high clock level as this gives best response uniformity.

Charges are amalgamated under the  $\emptyset$ 2 electrodes at the start of line transfer. Charge collection under only the  $\emptyset$ 2 (or  $\emptyset$ 1) electrodes is also possible.

The charge detection amplifiers A1 and A3 are optimised for large signal, high speed operation, whereas amplifiers A2 and A4 are optimised for very low noise under cooled slow-scan operation.

## **OPERATING SCHEMATIC** Charge Transfer to Section C

# **OPERATING SCHEMATIC** Charge Transfer to Sections C and D

### **OPERATING SCHEMATIC** Charge Transfer to Section D

OPERATING SCHEMATIC Charge Transfer in Sections C and D

# DETAIL OF VERTICAL LINE TRANSFER

FIRST LINE TRANSFER

Pulses should be approximately symmetrical and overlap at 50 - 70 % amplitude. For slow-scan operation, the rise and fall times are typically 1  $\mu s$  and 100 ns for sections A/B and C/D respectively. For high speed operation the timings for sections C/D can be reduced to 15 ns. The ØR width is typically 10 - 15% of the section C/D clock period.

6444A

LAST LINE TRANSFER

# OUTPUT AMPLIFIER SCHEMATICS Low Noise (A2, A4)

A $\emptyset$ 1/B $\emptyset$ A $\emptyset$ 2/B $\emptyset$ A $\emptyset$ 3/B $\emptyset$   $(\phi - 2) \mu s$ C $\emptyset$ 1/D $\emptyset$ C $\emptyset$ 2/D $\emptyset$ C $\emptyset$ 3/D $\emptyset$  $(\phi R1/2/3/4)$

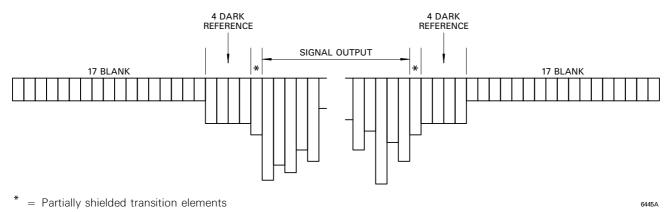

# LINE OUTPUT FORMAT

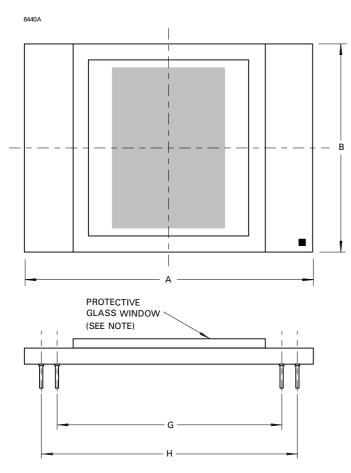

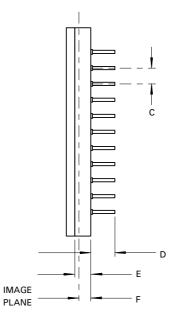

# **OUTLINE (All dimensions nominal)**

Not for inspection purposes

| Ref | Inches | Millimetres |  |

|-----|--------|-------------|--|

| A   | 1.800  | 45.72       |  |

| В   | 1.300  | 33.02       |  |

| С   | 0.100  | 2.54        |  |

| D   | 0.150  | 3.81        |  |

| Е   | 0.09   | 2.29        |  |

| F   | 0.066  | 1.68        |  |

| G   | 1.400  | 35.56       |  |

| Н   | 1.600  | 40.64       |  |

|     |        |             |  |

**Outline Note** The device is normally supplied with a temporary glass window for protection purposes. It can also be supplied with a fixed, quartz or fibre-optic window where required.

Millimetre dimensions have been derived from inches.

## **PIN CONNECTIONS (View on Pins)**

## **ORDERING CODE**

The ordering code to define a device in this series is constructed as follows:

Generic type indicates 770 horizontal elements -Y- Blemish grade: see data for grades available

-XXX Defines the package design and/or any special features relating to the CCD (presence or absence of antiblooming etc). Please discuss any such special requirements either with Marconi Applied Technologies or your local Marconi Applied Technologies representative.

Device variants are grouped accordingly:

- -001-199 Image Sensors (Room Temperature Tested) TV and room temperature testing. Standard device -002.

- -200-399 Scientific

All devices slow scan tested. Standard device -202.

- -400-499 Peltier Peltier cooled devices.

- -500-599 Unidentified

- -600-799 Intensified/fibre-optic coupled

- A device which has an intensifier and/or fibre-optic coupled to the CCD.

- -800-999 Specials

For a standard grade 1 device with a temporary window please order type number.

#### CCD05-20-1-202

A device coated to enhance UV response is also available, type number

#### CCD05-20-1-210

Please see separate data sheet for UV coating specification.

Whilst Marconi Applied Technologies has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. Marconi Applied Technologies accepts no liability beyond that set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of tubes or other devices in accordance with information contained herein.